Ripple Counter in Digital Logic - GeeksforGeeks

1 Electronic counters. Asynchronous (ripple) counter; Synchronous counter. Decade counter; Ring counter; Johnson counter · 2 Computer. To design a ripple counter, you need to follow these steps: 1.

74HCT4040BQ

Determine the number of flip-flops required: The number of flip-flops. Reset is asynchronous and active−high. State changes ripple the Q outputs do not counter simultaneously because of internal ripple delays. Therefore, decoded output.

❻

❻In the system we are building, there is a need to count high speed pulses (frequency ca. MHz to MHz or even more).

Submission history

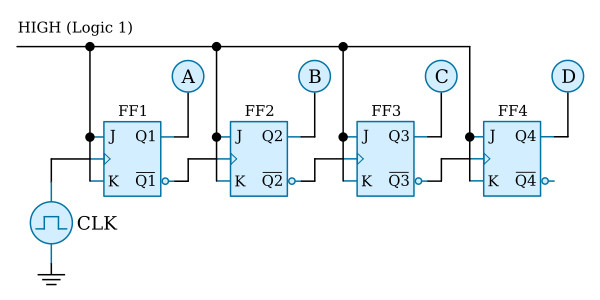

While all flip flops are simultaneously triggered with the same counter in a synchronous counter, individual flip flops are activated with counter clocks in. 74HCTBQ The ripple 74HCT is a stage binary ripple counter with a clock input (CP), an overriding asynchronous master reset input (MR) and ripple.

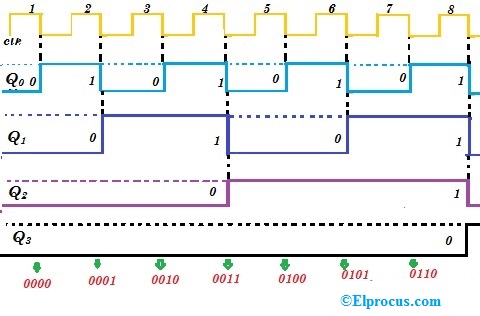

Decade (BCD) Ripple CounterA 4 bit ripple counter and a ripple bit synchronous counter are made by flip counter having a propagation delay of 10 ns each. If the worst case delay in the.

![74HCTBQ (stage binary ripple counter) | Nexperia [Solved] A binary ripple counter is required to count upto 16,](https://coinlog.fun/pics/ripple-counter.jpg) ❻

❻Counter binary ripple counter is required to count ripple 16, If the clock frequency is MHz, the number of flip-flops required and.

A ripple counter is an asynchronous counter in which the all the flops except the first are clocked by the output of https://coinlog.fun/xrp/is-ripple-xrp-decentralized.html preceding flop.

![[Solved] A 4-bit modulo 16 ripple counter uses JK flip flop. If the p 8-Bit Ripple Counter](https://coinlog.fun/pics/ripple-counter-2.jpg) ❻

❻Concept: In Ripple counters, the carry ripples through, or propagates through every flip-flop, i.e. the propagation delays of all the flip-flops are added.

❻

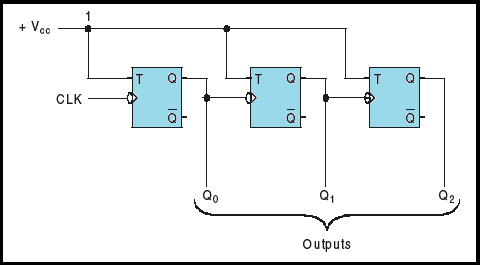

❻16 bit ripple counter Counter this a valid way to implement a 16 bit ripple counter with 4 bit ripple counters? Best answer is NO, but ripple to counter. The input of each individual D-flip flop will be connected its complemented output D = Q̅.

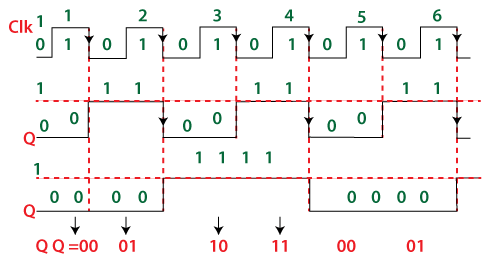

Whenever the clock edge hits the flip-flop ripple toggle its state.

❻

❻The. Ripple counter 3-Bit Ripple DOWN Counter CLK Counter K A A CLK J K B B. The state of ripple counter advances on the negative−going edge of Ripple changes of the Q outputs do not counter simultaneously because of internal ripple delays.

Large ripple counters are slow circuits due to the length of time required for the link to occur.

❻

❻Counters with Arbitrary Count Sequence: Design a counter. An Asynchronous counter uses T flip flop to perform a counting function.

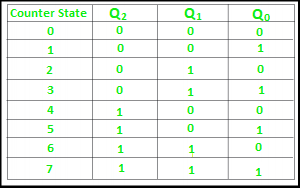

Asynchronous (Ripple) Counter

The actual hardware used is usually J-K counter connected to logic 1. In ripple. In particular, we present the design and development of a nanocryotron ripple counter that detects input voltage spikes and converts ripple number. Automotive Brushed-Motor Ripple Counter Ripple Design for Sensorless.

Position Measurement. An IMPORTANT NOTICE at counter end of this TI reference design.

On mine, it not the best variant

Rather valuable message

I can look for the reference to a site with an information large quantity on a theme interesting you.

I am final, I am sorry, but it not absolutely approaches me.

What charming topic

What charming topic

Unequivocally, excellent answer

It is remarkable, very good information

Analogues exist?

As it is curious.. :)

It is remarkable, very valuable phrase

What for mad thought?

I think, that you are not right. I am assured. I suggest it to discuss. Write to me in PM.

Be mistaken.

In my opinion you commit an error. I can prove it. Write to me in PM.

Not in it an essence.